厦门国科安芯科技有限公司

**MCU芯片-AS32S401 数据手册**

## 目录

|      |                           |    |

|------|---------------------------|----|

| 1    | 规格说明                      | 1  |

| 2    | 功能概述                      | 4  |

| 2.1  | RISC-V 处理器                | 5  |

| 2.2  | 存储器                       | 5  |

| 2.3  | 内存保护单元 (MPU)              | 5  |

| 2.4  | 中断                        | 5  |

| 2.5  | 时钟和复位管理                   | 6  |

| 2.6  | 启动模式                      | 7  |

| 2.7  | 直接存储器访问控制器 (DMA)          | 7  |

| 2.8  | 通用输入/输出接口 (GPIO)          | 7  |

| 2.9  | 通用异步收发器 (UART)            | 8  |

| 2.10 | 内部集成电路总线接口 (IIC)          | 9  |

| 2.11 | 串行外设接口 (SPI)              | 9  |

| 2.12 | 局域互连网络 (LIN)              | 10 |

| 2.13 | 定时器 (TIMER)               | 11 |

| 2.14 | 以太网                       | 12 |

| 2.15 | 控制器局域网络 (CAN)             | 12 |

| 2.16 | 循环冗余校验计算单元 (CRC)          | 13 |

| 2.17 | 正交编码器接口 (QEI)             | 14 |

| 2.18 | 模数转换器 (ADC)               | 14 |

| 2.19 | 数模转换器 (DAC)               | 15 |

| 2.20 | 看门狗 (WDT)                 | 15 |

| 2.21 | 1553B 控制器 (MIL-STD-1553B) | 16 |

| 3    | 存储器地址映射                   | 17 |

| 4    | 引脚说明                      | 19 |

| 5    | 文档历史版本                    | 25 |

## 1 规格说明

AS32X401 微控制器是一种基于 32 位 RISC-V 处理器的高性能高可靠的通用微控制器。其核心采用具备双核锁步功能的 RISC-V 处理器，工作频率最高可达 120MHz。

AS32X401 微控制器内置双备份 QSPI Flash，片上存储容量可达 160KB，其中 ICACHE 16KB、DTCM 16KB、分布式 SRAM 128KB。

AS32X401 微控制器提供了丰富的外设接口，均挂载在 AHB 总线上。设备最多可支持 80 路 GPIO，提供了 4 路标准 UART 接口、1 路调试 UART、4 路 SPI 接口、4 路 IIC 接口、1 路 LIN 接口、2 路 CAN FD 总线接口、2 路 12 位 DAC 接口、2 个 12 位 ADC 接口、3 个 16 位高级定时器、2 个 QEI 接口、1 路 10/100M 以太网接口、2 路 MIL-STD-1553B 接口。

### 处理器内核：

- 基于 RISC-V 的 32 位 CPU

- 32 位 RISC-V RV32IMZicsr 指令集

- 工作频率：120MHz

- 单周期双核锁步架构设计，可抗共模故障

- 采用 fail-safe 设计，支持单周期错误回滚

- 内部存储和总线采用低功耗 SECDED 编码进行自动纠检错

- 系统控制模块采用三模冗余设计

### 存储器

- 双备份 QSPI Flash

- 128KB SRAM

- 16KB 高速缓冲指令存储器 (ICACHE)

- 16KB 数据紧耦合内存 (DTCM)

### 模拟模块

- 2 个 12bit ADC 接口，16 路复用输入通道

- 2 路 12bit DAC 接口

## DMA 定时器

- 16 通道 DMA 控制器

- 3 个 16 位高级定时器，每个定时器多达 6 个用于输入捕获/输出比较/PWM 或单脉冲计数的通道

- 1 个看门狗定时器

## 数字接口

- 多达 4 个标准 UART 接口

- 多达 4 个 SPI 接口

- 多达 4 路 IIC 接口

- 1 路 LIN 接口

- 2 路 CAN FD 总线接口

- 2 个 QEI 接口

- 1 路 10/100M 以太网接口

- 2 路 MIL-STD-1553B 接口

## 抗辐照（商业航天级）

- SEU :  $\geq 75 \text{ Mev.cm}^2/\text{mg}$  或  $10^{-5} \text{ 次/器件.天}$

- SEL :  $\geq 75 \text{ Mev.cm}^2/\text{mg}$

## 工作环境

- 封装工艺: LQFP144

- 尺寸: 20\*20mm, pitch 0.5mm

芯片型号为:

| 芯片类型 | 芯片型号         | 等级    | 封装      | 备注 |

|------|--------------|-------|---------|----|

| MCU  | AS32I401VHT6 | 工业级   | LQFP144 |    |

| MCU  | AS32S401VHT2 | 商业航天级 | LQFP144 |    |

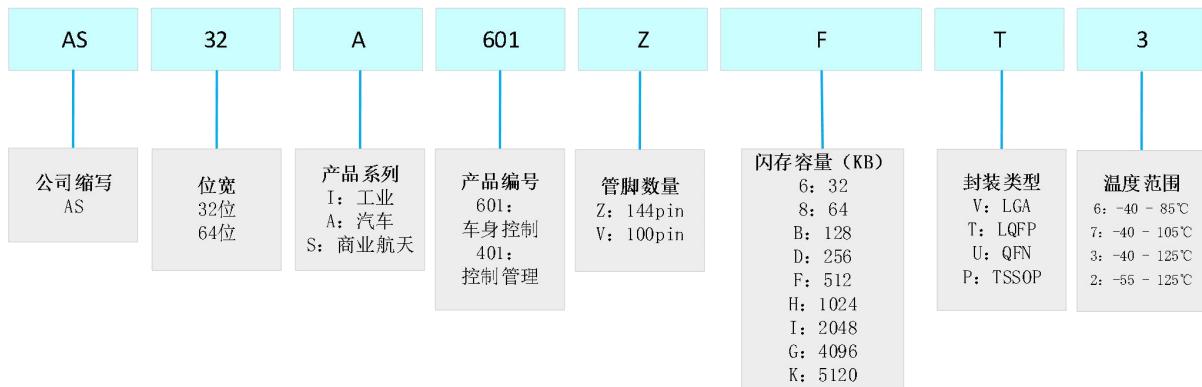

## 芯片命名规则

## 2 功能概述

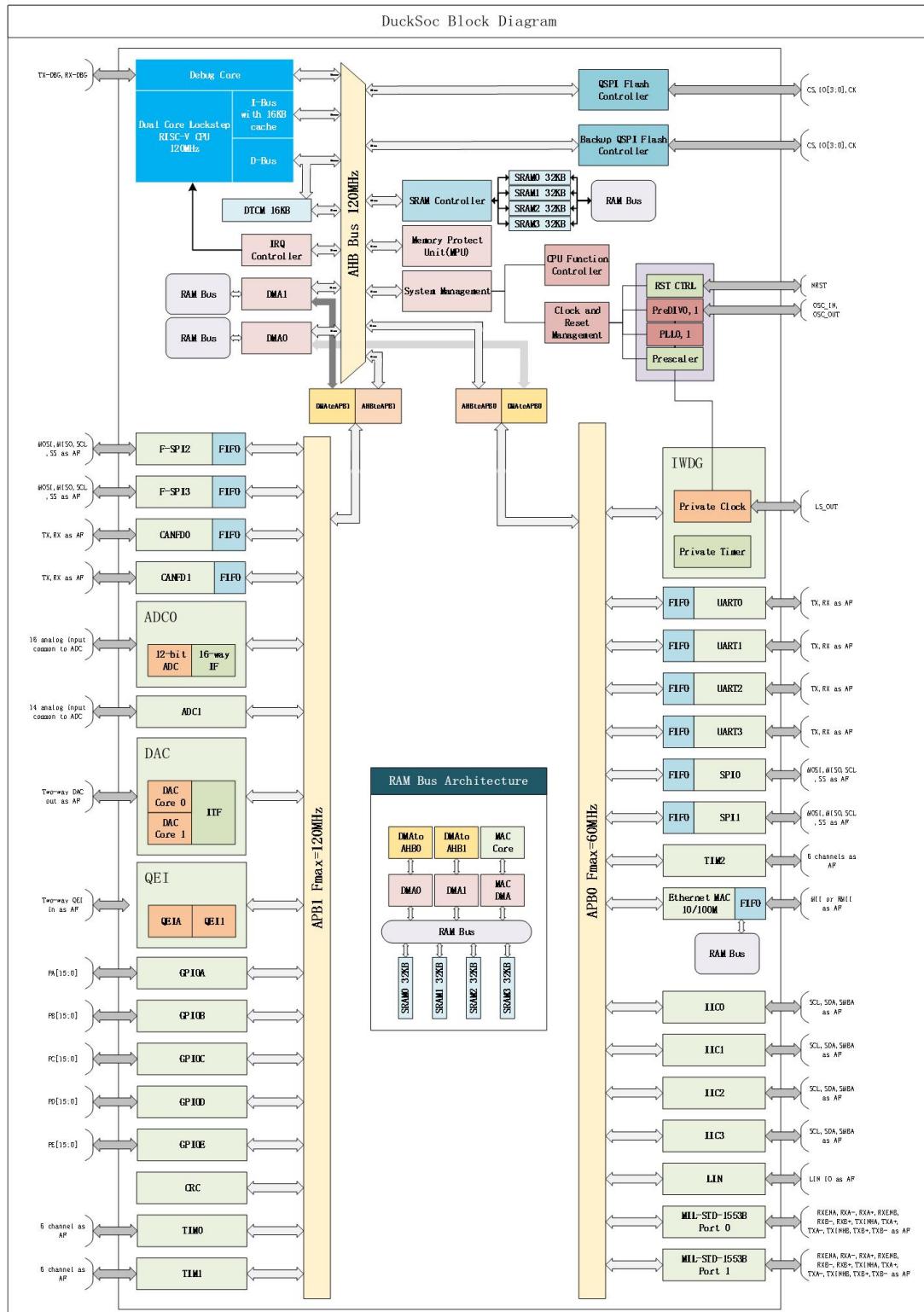

图 2.1 AS32S401 系统架构图

## 2.1 RISC-V 处理器

AS32I401 微控制器是一款基于 32 位 RISC-V 处理器的高性能高可靠的嵌入式微控制器。处理器内核采用带双核锁步功能的 RISC-V (Rv32IMZicsr) 处理器内核，具备单 bit 编码纠错、多 bit 编码检错单周期回滚的特点，具备较好的可靠性。

## 2.2 存储器

- 双备份 QSPI Flash

- 128KB SRAM

- 16KB 高速缓冲指令存储器 (ICACHE)

- 16KB 数据紧耦合内存 (DTCM)

## 2.3 内存保护单元 (MPU)

AS32I401 为用户提供了 MPU 以对特定地址的内存/外设进行保护。MPU 可用于禁止程序破坏关键任务（例如操作系统内核）的数据，锁定 SRAM 内存区域（读保护+写保护）以防止代码注入攻击等操作来保护整个嵌入式系统，进而提升系统的鲁棒性与安全性。

- 可编程的保护宽度，从 32B 到 32KB 区间的保护宽度；

- 16 个独立的内存保护通道，各个通道之间的保护区域可叠加；

- 单周期快速异常响应；

- 在命中时锁定数据通道以保证不出现非法访问情况；

- 支持三种保护模式：读保护，写保护，或锁定区域（读保护+写保护）。

## 2.4 中断

AS32I401 支持 32 个中断源输入，支持软件和硬件两种保存恢复现场方式，可以通过硬件保存恢复现场使能位控制，最多可支持 8 级硬件保存恢复现场。中断包括外设、CSR 软件中断和 CSR 定时器中断。中断入口为向量模式，各中断请求有单独的用户配置的入口函数地址。PLIC 为中断控制器，支持中断的使能，优先级设置。

- 当前输入支持 32 个中断源，每个中断源分配一个 ID，ID 号 0 代表无中断；

- 优先级支持软件设置，共计 0~31 级，可以设置为相同优先级，0 级最高，优先级一样时，ID 号小的先执行；

- 输出也是单周期脉冲信号，相同时间只有一个最高优先级中断输出，执行中断函数时不响应相同中断；

- 中断源全为上升沿触发；

- 中断为向量模式（硬件中断模式）；

- 支持中断嵌套（保存现场和恢复现场时不支持中断嵌套）；

- 每一中断源都有单独的使能位，注意区别于接口私有的中断使能，这两种需要全部开启；

- 支持中断优先级阈值设置。

## 2.5 时钟和复位管理

AS32I401 由一个 20MHz 无源晶体振荡器提供时钟。该时钟源作为一对互为备份的 PLL 使用，在其中一个损坏时可自动切换到另一个 PLL，其最高可倍频到 240MHz。

预分频器允许 CPU 与 AHB 时钟域最高使用 120MHz 的时钟频率，允许高速 APB 域（APB1）最高使用 120MHz 的时钟频率，低速 APB 域（APB0）最高使用 60MHz 的时钟频率。

AS32I401 系统控制复位的方式总共有四种：外部复位、看门狗复位、调试单元复位与 SMU 控制复位。其中外部复位通过外部控制信号进行复位，复位整个系统，看门狗复位作用于系统除了 SMU 之外的所有部分，而调试单元复位只作用于 CPU，SMU 控制复位可编程控制复位除其本身外所有部分。

## 2.6 启动模式

AS32I401 提供了三种引导源，可通过启动引脚（BOOT）设置进行选择：

- 从主份 QSPI Flash 启动；

- 从备份 QSPI Flash 启动；

- 从内部 SRAM 启动。

## 2.7 直接存储器访问控制器（DMA）

DMA 控制器提供了一种硬件的方式在外设和存储器之间或者存储器和存储器之间传输数据，而无需 CPU 的介入，从而使 CPU 可以专注在处理其他系统功能上。DMA 控制器有 16 个通道（DMA0、DMA1 各有 8 个通道）。每个通道都是专门用来处理一个或多个外设的存储器访问请求的。DMA 控制器内部实现了一个仲裁器，用来仲裁多个 DMA 请求。

DMA 控制器使用独立的外设总线。在大多数情况下 DMA 可与 CPU 同时访问同样的地址空间。仅当 DMA 和 CPU 访问同样的外设时，DMA 访问可能会阻挡 CPU 访问系统总线几个总线周期。外设总线矩阵中实现了循环仲裁算法来分配 DMA 与 CPU 的访问权，它可以确保 CPU 得到至少一半的外设带宽。

DMA 可以用于的外设：UART、IIC、SPI、ADC、DAC。

## 2.8 通用输入/输出接口（GPIO）

AS32I401 最多可支持 80 个通用 I/O 引脚（GPIO），分别为 PA0~PA15，PB0~PB15，PC0~PC15，PD0~PD15 和 PE0~PE15，各片上设备用其来实现逻辑输入/输出功能。每个 GPIO 端口有相关的控制和配置寄存器以满足特定应用的需求。外设 GPIO 引脚上都有其独立的中断控制。

GPIO 端口和其他的备用功能（Afs）共用引脚，在特定的封装下获得最大的灵活性。GPIO 引脚通过配置相关的寄存器可以用作备用功能引脚，备用功能输入/输出都

可。每个 GPIO 引脚可以由软件配置为输出（推挽或开漏）、输入、外设的备用功能或者模拟模式。每个 GPIO 引脚都可以配置为上拉、下拉或无上拉/下拉。

## 2.9 通用异步收发器 (UART)

AS32I401 提供了 4 个通用异步收发器 (UART)，可灵活方便进行串行数据交换，数据帧可以通过全双工异步的方式进行传输。

UART 提供了可编程的波特率发生器，能对系统时钟进行分频产生 UART 发送器和接收器所需的具体频率。

UART 支持 DMA 功能，可以实现高速率的数据通信，减轻 CPU 的负担。

- NRZ 标准格式

- 全双工异步通信

- 半双工单线通信

- 可编程的波特率产生器

- 由 APB0 时钟分频产生时钟

- 可调整的过采样倍率

- 完全可编程的串口特性

- 偶校验位、奇校验位、无校验位的生成/检测

- 数据位 (7 或 8 位)

- 256 位读/写 FIFO

- DMA 访问数据缓冲区

- 传输检测标志：接收缓冲区不为空 (RXNE)、发送缓冲区为空 (TXE)、发送完成 (TC)、接收完成 (IDLE)

- 错误检测标志：过载错误 (ORES)，帧格式错误 (FERS)，奇偶校验错误 (PERS)

## 2.10 内部集成电路总线接口（IIC）

AS32I401 提供了 4 个 IIC 总线接口，具有符合工业标准的两线串行制接口，可用于 MCU 和外部 IIC 设备的通讯。IIC 总线使用两条串行线：串行数据线 SDA 和串行时钟线 SCL。

IIC 总线接口支持主从模式，可在主从及之间进行双向数据传输。IIC 总线接口在标速模式下可提供最高 100KHz 的传输速率，在快速模式下，可提供最高 400KHz 的传输速率，支持 PMBus（电源管理总线）。

IIC 接口模块支持 DMA 模式，可有效减轻 CPU 的负担。

- 同一接口既可实现主机功能又可实现从机功能

- 主从机之间的双向数据传输

- 支持 7 位的地址寻址模式

- 支持 IIC 多主机模式

- 从机模式下可配置的 SCL 主动拉低

- 支持 DMA 模式

- 三种中断：发送中断、接收中断与传输步骤中断

## 2.11 串行外设接口（SPI）

AS32I401 提供了 4 个 SPI 接口，支持半双工/全双工的同步串行通信。SPI 接口支持主从模式，配置为主机或从机模式。配置为主机模式时，它可为外部从器件提供通信时钟（SCK），SPI2 和 SPI3 接口支持 4 个从机，拥有 4 个从机片选，SPI0 和 SPI1 支持 1 个从机。

SPI 接口支持 DMA 功能。

- 支持 Motorola 模式串行外设接口（SPI）

- 4 线全双工同步传输（3 线半双工）

- 4~32 位传输帧格式选择

- SPI 时钟速率可配置

- 主模式或从模式操作

- 主模式时最高频率 PCLK/2

- 从模式时最高频率 PCLK/8

- 数据发送顺序 MSB 在前

- 可编程的时钟极性和相位

- 可触发中断的专用发送和接收标志

## 2.12 局域互联网络 (LIN)

AS32I401 支持 1 路 LIN 接口。

LIN 是基于 UART/SCI 的低成本串行通信协议，可用于汽车、家电、办公设备等多种领域。网络由一个主机节点和多个从机节点构成，主机节点（Master Node）包含主机任务（Master Task）和从机任务（Slave Task），从机节点（Slave Node）只包含从机任务。LIN 协议规定最大位速率为 20kbps。由于物理层限制，一个 LIN 网络最多可以连接 16 个节点，典型应用一般都在 12 个节点以下，主机节点有且只有一个，从机节点有 1 到 15 个。

- 主机写（发送帧头和应答帧）

- 主机读（只发帧头）

- 从机写（发送应答帧）

- 从机任务发送或者接收数据端和校验和

- 同步间隔端和同步段检测，帧头检测

- 可编程波特率及自动波特率检测

- 数据场字节数配置，支持 1~8 字节

- 标准校验和增强校验设置

- 同步间隔段宽度, 间隔界定符宽度, 应答间隔, 字节间距, 帧间隔宽度设置

- 总线错误检测

- P1, P0 校验错误

- 校验和错误

- 应答错误检测 (帧响应时被新来帧打断)

- 中断输出

- 总线接收数字滤波

- P1, P0 校验位发送和接收自动计算

- 发送和接收校验和自动计算

## 2.13 定时器 (TIMER)

AS32I401 提供了 3 组高级定时器。高级定时器包含一个 16 位自动重载计数器, 该计数器由可编程预分频器进行驱动, 并支持多种计数模式。该定时器为 6 通道定时器, 支持输入捕获、输出比较、单脉冲模式, 可实现测量输入信号的脉冲宽度、生成 PWM 波形等功能。定时器的主要特征如下:

- 总通道数: 6;

- 16 位递增计数、递减计数、中心计数的自动重载计数器;

- 16 位可编程预分频器, 用于对计数器时钟进行分频, 可在运行中修改, 分频系数范围为 1~65536;

- 自动重装载功能;

- 支持单脉冲模式;

- 每个通道可配置: 输入捕获模式、输出比较模式、可编程 PWM 模式。

## 2.14 以太网

AS32I401 提供了 1 路 10M/100M 以太网接口。MAC 接口实现了由 IEEE 802.3 定义的媒体访问控制（MAC）通过以太网连接的碰撞检测（CSMA/CD）算法。与外部主机的通信是通过一组控制和状态寄存器和针对外部共享 RAM 的直接内存访问（DMA）控制器来实现的。MAC 接口通过 DMA 方式与主机实现数据发送。它自动获取发送缓冲区数据和存储接收缓冲区数据到外部 RAM。它通过对接收和发送描述符链表的管理，实现多种内存分配方案。MAC 接口内部 RAM 被用作可配置的 FIFO 存储器块，并且有单独的用于发送和接收进程的存储器块。

- 支持外部 PHY 接口实现 10/100Mbit/s 数据传输速率；

- 通过符合 IEEE 802.3 的 MII 接口与外部快速以太网 PHY 进行通信；

- 支持全双工和半双工操作；

- 报头和帧起始数据（SFD）在发送路径中插入、在接收路径中删除；

- 可逐帧控制 CRC 和 PAD 自动生成；

- 接收帧时可自动去除 PAD/CRC；

- 支持多种灵活的地址过滤模式；

- 两组缓存 FIFO（接收 FIFO 和发送 FIFO）；

- DMA 在内存和 MAC 的缓存区进行数据搬移。

## 2.15 控制器局域网络（CAN）

AS32I401 提供了 2 路 CAN 接口。CAN 接口根据 ISO11898-1: 2015 和 Bosch CAN FD 规范进行通信。连接到物理层需要额外的收发器硬件。

所有有关处理消息的函数都由接收处理程序和发送处理程序实现。接收处理程序管理消息接受过滤，将接收到的消息从 CAN 核心发送到消息 RAM，以及提供接收消息状态信息。发送处理程序负责将发送消息从消息 RAM 发送到 CAN 核心，并提供发送状态信息。

---

接受过滤通过最多 32 个过滤器元素的组合来实现，其中每个元素可以配置为范围、位掩码或专用 ID 过滤器。

- 设计符合 ISO11898-1/2015 规范；

- 支持 CAN 和 CAN FD 帧；

- 支持 ISO11899: 2015 规范中指定的 CAN FD 帧格式；

- 支持 64 字节 CAN FD 帧；

- 支持可变数据速率高达 8Mb/s；

- 支持正常数据速率 1Mb/s；

- 支持高达三个数据位的发射器延迟补偿；

- 支持可配置的发送和接受邮箱缓冲区；

- 支持两个深度为 64 帧消息的缓冲与 32 个 ID 过滤掩码；

- 支持低 ID 的消息优先发送；

- 支持待发送消息消除；

- 支持快速数据速率时的单独错误记录。

## 2.16 循环冗余校验计算单元 (CRC)

AS32I401 内部集成了一个 CRC 计算单元。循环冗余校验（Cyclic Redundancy Check, CRC）是一种根据网络数据包或计算机文件等数据产生简短固定位数校验码的一种信道编码技术，主要用来检测或校验数据传输或者保存后可能出现的错误。它是利用除法及余数的原理来作错误侦测的。

CRC（循环冗余校验）计算单元使用一个多项式发生器从 8 位/16 位/32 位的数据字中产生 CRC 码。CRC 计算单元主要特征如下：

- 使用位数可预设定的（7 位、8 位、16 位和 32 位）完全可编程多项式；

- 可处理 8 位、16 位、32 位数据大小；

- 可编程 CRC 初始值；

- 单输入/输出 32 位数据寄存器；

- 输入缓冲器可避免计算期间发生总线阻塞；

- I/O 数据的可逆性选项；

- 支持异或计算。

## 2.17 正交编码器接口 (QEI)

AS32I401 提供了 2 个 QEI 接口。正交编码器接口 (QEI) 模块提供了用于获得机械位置数据的增量式编码器的接口。正交编码器（也称为增量式编码器或光电式编码器）用于检测旋转运动系统的位置和速度。正交编码器可用于实现多种电机控制应用的闭环控制，例如开关磁阻 (Switched Reluctance, SR) 电机和交流感应电机 (AC Induction Motor, ACIM)。

- 两个相位信号 (QEA 和 QEB) 和一个索引信号 (INDX)

- 带有方向变化中断的运动方向检测

- 可编程的 QEA, QEB 和 INDX 输入噪声过滤器

- 32 位速度和位置寄存器

- 两种位置更新模式 (x2 和 x4)

- 速度测量与可编程脉冲分频后高速速度测量

- 位置计数器中断

- 速度更新中断

## 2.18 模数转换器 (ADC)

AS32I401 提供了 2 个 12 位模拟/数字转换器 (ADC)，具有 16 个多路复用通道，可以转换来自多个外部通道的模拟信号。模拟看门狗允许应用程序来检测输入电压是否超出用户设定的高低阈值。各种通道的 A/D 转换可以配置成单次、连续、扫描或间

---

断转换模式。ADC 转换的结果可以按照左对齐或右对齐的方式存储在 16 位数据寄存器中。ADC 支持使用 DMA 操作。

## 2.19 数模转换器 (DAC)

AS32I401 提供了 2 个 12 位模拟/数字转换器 (DAC)。DAC 可以将 12 位的数字数据转换为外部引脚上的电压输出。当使能外部触发，DMA 可被用于更新输入端数字数据。在输出电压时，可以利用 DAC 输出缓冲区来获得更高的驱动能力。两个 DAC 可以独立或并发工作。DAC 支持下述功能：

- 12 位分辨率，数据左对齐或右对齐；

- 同步更新转换；

- 外部事件触发转换；

- 输入参考电压，VREF+；

- 噪声波生成 (LSFR 噪声模式和三角噪声模式)；

- 支持 DMA 操作；

- 双 DAC 并发模式。

## 2.20 看门狗 (WDT)

看门狗计时器 (WDT) 用于防止软件陷入死锁时的系统锁定。它具有一个 32 位向下计数器，允许外部独立时钟输入，预置了一个 12 位的预分频器。它只能生成一般重置或处理器重置。此外，它可以在处理器处于调试模式或睡眠模式 (空闲模式) 时停止。

- 支持 32 位看门狗定时器；

- 预置分频器，分频器的值最高到 1024；

- 支持独立外部时钟输入 20MHz；

- 支持外部输入复位 (喂狗)。

## 2.21 1553B 控制器（MIL-STD-1553B）

AS32I401 支持 2 个 1553B 总线控制器，分别为 1553B0 和 1553B1。

1553B 总线采用异步数据传输方式，码速率 1Mbps，数据编码采用曼彻斯特 II 型码，差分传输，一般情况下采用屏蔽双绞线作为传输介质。

- 支持 BC、RT、BM 三种模式

- 输入时钟 20M，内部生成发送时钟 1M

- 寄存器配置模式

- 中断日志功能

- 可编程的消息延迟

- 循环缓存模式

- 专用 memory 的大小为 16k 字节，用于存储消息列表、数据和中断日志列表

### 3 存储器地址映射

表 3.1 AS32I401 存储器地址映射表

| 空间内容               | 地址                      | 空间大小  |

|--------------------|-------------------------|-------|

| FLASH              | 0x0000_0000~0x0FFF_FFFF | 256MB |

| BK_FLASH           | 0x5000_0000~0x5FFF_FFFF | 256MB |

| RAM                | 0x1000_0000~0x1FFF_FFFF | 256MB |

| SRAM0              | 0x1000_0000~0x1000_7FFF | 32KB  |

| SRAM1              | 0x1000_8000~0x1000_FFFF | 32KB  |

| SRAM2              | 0x1001_0000~0x1001_7FFF | 32KB  |

| SRAM3              | 0x1001_8000~0x1001_FFFF | 32KB  |

| SMU                | 0x2000_0000~0x21FF_FFFF | 32MB  |

| DMA0               | 0x2200_0000~0x22FF_FFFF | 16MB  |

| DMA1               | 0x2300_0000~0x23FF_FFFF | 16MB  |

| MPU                | 0x2400_0000~0x24FF_FFFF | 16MB  |

| ICACHE (二路组相连)     |                         | 16KB  |

| PLIC               | 0x2500_0000~0x25FF_FFFF | 16MB  |

| DTCM               | 0x2600_0000~0x2600_7FFF | 16KB  |

| UART0              | 0x3000_0000~0x30FF_FFFF | 16MB  |

| UART1              | 0x3100_0000~0x31FF_FFFF | 16MB  |

| UART2              | 0x3200_0000~0x32FF_FFFF | 16MB  |

| UART3              | 0x3300_0000~0x33FF_FFFF | 16MB  |

| SPI0               | 0x3400_0000~0x34FF_FFFF | 16MB  |

| SPI1               | 0x3500_0000~0x35FF_FFFF | 16MB  |

| TIM2               | 0x3600_0000~0x36FF_FFFF | 16MB  |

| MAC                | 0x3700_0000~0x37FF_FFFF | 16MB  |

| IIC0               | 0x3800_0000~0x38FF_FFFF | 16MB  |

| IIC1               | 0x3900_0000~0x39FF_FFFF | 16MB  |

| IIC2               | 0x3A00_0000~0x3AFF_FFFF | 16MB  |

| IIC3               | 0x3B00_0000~0x3BFF_FFFF | 16MB  |

| LIN                | 0x3C00_0000~0x3CFF_FFFF | 16MB  |

| MIL-STD-1553B 总线 0 | 0x3D00_0000~0x3DFF_FFFF | 16MB  |

| MIL-STD-1553B 总线 1 | 0x3E00_0000~0x3EFF_FFFF | 16M   |

| WATCHDOG           | 0x3F00_0000~0x3FFF_FFFF | 16M   |

| SPI2               | 0x4000_0000~0x40FF_FFFF | 16M   |

| SPI3               | 0x4100_0000~0x41FF_FFFF | 16M   |

| CAN FD0            | 0x4200_0000~0x42FF_FFFF | 16M   |

| 空间内容    | 地址                      | 空间大小 |

|---------|-------------------------|------|

| CAN FD1 | 0x4300_0000~0x43FF_FFFF | 16M  |

| ADC0    | 0x4400_0000~0x44FF_FFFF | 16M  |

| ADC1    | 0x4500_0000~0x45FF_FFFF | 16M  |

| GPIOA   | 0x4600_0000~0x46FF_FFFF | 16M  |

| GPIOB   | 0x4700_0000~0x47FF_FFFF | 16M  |

| GPIOC   | 0x4800_0000~0x48FF_FFFF | 16M  |

| GPIOD   | 0x4900_0000~0x49FF_FFFF | 16M  |

| GPIOE   | 0x4A00_0000~0x4AFF_FFFF | 16M  |

| CRC     | 0x4B00_0000~0x4BFF_FFFF | 16M  |

| TIM0    | 0x4C00_0000~0x4CFF_FFFF | 16M  |

| TIM1    | 0x4D00_0000~0x4DFF_FFFF | 16M  |

| DAC     | 0x4E00_0000~0x4EFF_FFFF | 16M  |

| QEI     | 0x4F00_0000~0x4FFF_FFFF | 16M  |

## 4 引脚说明

| Pin | Pin name      | Pin type | IO  | Alternate functions 0 | Alternate functions 1 | Additional functions |

|-----|---------------|----------|-----|-----------------------|-----------------------|----------------------|

| 1   | VSS           | S        | —   | —                     | —                     | —                    |

| 2   | VDD           | S        | —   | —                     | —                     | —                    |

| 3   | B_QSPI_DIO[1] | I/O      | TTa | —                     | —                     | —                    |

| 4   | B_QSPI_DIO[2] | I/O      | TTa | —                     | —                     | —                    |

| 5   | B_QSPI_CSN    | I/O      | TTa | —                     | —                     | —                    |

| 6   | PC13          | I/O      | FT  | TIM2_CH2              | —                     | —                    |

| 7   | PC14          | I/O      | FT  | TIM2_CH3              | —                     | —                    |

| 8   | PC15          | I/O      | FT  | TIM2_CH4              | —                     | —                    |

| 9   | NRST          | I        | RST | —                     | —                     | —                    |

| 10  | B_QSPI_DIO[0] | I/O      | TTa | —                     | —                     | —                    |

| 11  | B_QSPI_CLK    | I/O      | TTa | —                     | —                     | —                    |

| 12  | B_QSPI_DIO[3] | I/O      | TTa | —                     | —                     | —                    |

| 13  | VSS           | S        | —   | —                     | —                     | —                    |

| 14  | VDD           | S        | —   | —                     | —                     | —                    |

| 15  | VSS_IO        | S        | —   | —                     | —                     | —                    |

| 16  | PC2           | I/O      | TTa | ADC1_RTRG             | ADC2_RTRG             | ADC12_IN12           |

| 17  | PC0           | I/O      | TTa | —                     | —                     | ADC12_IN10           |

| 18  | PC1           | I/O      | TTa | —                     | —                     | ADC12_IN11           |

| 19  | PC3           | I/O      | TTa | ADC1_LTRG             | ADC2_LTRG             | ADC12_IN13           |

| 20  | VDD_IO/AVDD33 | S        | —   | —                     | —                     | —                    |

| 21  | PA0           | I/O      | TTa | DAC_TRG1              | —                     | ADC12_IN0/WKUP       |

| 22  | PA1           | I/O      | TTa | DAC_TRG2              | —                     | ADC12_IN1            |

| 23  | PA2           | I/O      | TTa | ETH_TXEN              | —                     | ADC12_IN2            |

| 24  | PA3           | I/O      | TTa | ETH_TXER              | —                     | ADC12_IN3            |

| 25  | VSS           | S        | —   | —                     | —                     | —                    |

| 26  | VDD           | S        | —   | —                     | —                     | —                    |

| 27  | PA4           | I/O      | TTa | —                     | —                     | ADC1_IN14/DAC_OUT1   |

| 28  | PA5           | I/O      | TTa | —                     | —                     | ADC1_IN15/DAC_OUT2   |

| 29  | PA6           | I/O      | TTa | ETH_RXDV              | —                     | ADC12_IN4            |

| 30  | PA7           | I/O      | TTa | ETH_TXCLK             | —                     | ADC12_IN5            |

| 31  | VSS_IO/AVSS33 | S        | —   | —                     | —                     | —                    |

| 32  | PC4           | I/O      | TTa | ETH_RXCRS             | —                     | ADC12_IN6            |

| 33  | PC5           | I/O      | TTa | ETH_RXCLK             | —                     | ADC12_IN7            |

| 34  | PB0           | I/O      | TTa | ETH_RXCOL             | —                     | ADC12_IN8            |

| 35  | PB1           | I/O      | TTa | ETH_RXER              | —                     | ADC12_IN9            |

| 36  | PB2           | I/O      | FT  | —                     | —                     | BOOT1                |

|    |                       |     |    |                       |          |   |

|----|-----------------------|-----|----|-----------------------|----------|---|

| 37 | AVSS33/DVSS33         | S   | —  | —                     | —        | — |

| 38 | AVDD33/DVDD3<br>3     | S   | —  | —                     | —        | — |

| 39 | VREFP                 | S   | —  | —                     | —        | — |

| 40 | VREFN                 | S   | —  | —                     | —        | — |

| 41 | ADC_IB1U              | S   | —  | —                     | —        | — |

| 42 | DVSS12_ADC            | S   | —  | —                     | —        | — |

| 43 | DVDD12_ADC            | S   | —  | —                     | —        | — |

| 44 | DVSS12_PLL            | S   | —  | —                     | —        | — |

| 45 | AVSS12_PLL            | S   | —  | —                     | —        | — |

| 46 | DVDD12_PLL            | S   | —  | —                     | —        | — |

| 47 | AVDD12_PLL            | S   | —  | —                     | —        | — |

| 48 | VSS_IO_OSC            | S   | —  | —                     | —        | — |

| 49 | OSC_IN                | I   | —  | —                     | —        | — |

| 50 | OSC_OUT               | I   | —  | —                     | —        | — |

| 51 | VDD_IO/VDD_IO<br>_OSC | S   | —  | —                     | —        | — |

| 52 | PE7                   | I/O | FT | ETH_RXD0              | CAN1_RX  | — |

| 53 | PE8                   | I/O | FT | ETH_RXD1/CAN1_<br>TX  | —        | — |

| 54 | PE9                   | I/O | FT | ETH_RXD2              | UART0_RX | — |

| 55 | PE10                  | I/O | FT | ETH_RXD3/UART0<br>_TX | —        | — |

| 56 | VSS                   | S   | —  | —                     | —        | — |

| 57 | VSS_IO                | S   | —  | —                     | —        | — |

| 58 | PE11                  | I/O | FT | ETH_MDC/UART1<br>_RX  | —        | — |

| 59 | PE12                  | I/O | FT | ETH_MDIO              | UART1_TX | — |

| 60 | PE13                  | I/O | FT | ETH_TXD3/QEI0_A       | —        | — |

| 61 | PE14                  | I/O | FT | ETH_TXD2/QEI0_B       | —        | — |

| 62 | VDD                   | S   | —  | —                     | —        | — |

| 63 | VDD_IO                | S   | —  | —                     | —        | — |

| 64 | PE15                  | I/O | FT | ETH_TXD1/QEI0_I<br>D  | —        | — |

| 65 | PB10                  | I/O | FT | ETH_RXD0              | —        | — |

| 66 | PB11                  | I/O | FT | LIN                   | —        | — |

| 67 | PB12                  | I/O | FT | ETH_SCLK              | UART2_TX | — |

| 68 | VSS_IO                | S   | —  | —                     | —        | — |

| 69 | PB13                  | I/O | FT | ETH_SCS/UART2_<br>RX  | —        | — |

| 70 | PB14                  | I/O | FT | ETH_SDI               | —        | — |

|    |        |     |    |                         |                  |   |

|----|--------|-----|----|-------------------------|------------------|---|

| 71 | PB15   | I/O | FT | ETH_SDO                 | —                | — |

| 72 | PD8    | I/O | FT | SPI3_CS                 | 1553B1_A_IN_EN   | — |

| 73 | VSS    | S   | —  | —                       | —                | — |

| 74 | VDD_IO | S   | —  | —                       | —                | — |

| 75 | PD9    | I/O | FT | SPI3_SCK                | 1553B1_A_IN_P    | — |

| 76 | PD10   | I/O | FT | SPI3_MOSI               | 1553B1_A_IN_N    | — |

| 77 | PD11   | I/O | FT | SPI3_MISO               | 1553B1_B_IN_EN   | — |

| 78 | PD12   | I/O | FT | SPI3_MCS1/1553B1_B_IN_P | —                | — |

| 79 | VSS_IO | S   | —  | —                       | —                | — |

| 80 | VDD    | S   | —  | —                       | —                | — |

| 81 | PD13   | I/O | FT | SPI3_MCS2/1553B1_B_IN_N | —                | — |

| 82 | PD14   | I/O | FT | SPI3_MCS3               | 1553B1_A_OUT_P   | — |

| 83 | PD15   | I/O | FT | QEI1_A/1553B1_A_OUT_N   | —                | — |

| 84 | PC6    | I/O | FT | QEI1_B/1553B1_B_OUT_P   | —                | — |

| 85 | PC7    | I/O | FT | QEI1_ID/1553B1_B_OUT_N  | —                | — |

| 86 | VDD_IO | S   | —  | —                       | —                | — |

| 87 | VSS    | S   | —  | —                       | —                | — |

| 88 | VDD    | S   | —  | —                       | —                | — |

| 89 | PC8    | I/O | FT | IIC3_SCL                | 1553B1_A_OUT_TIN | — |

| 90 | PC9    | I/O | FT | IIC3_SDA                | 1553B1_B_OUT_TIN | — |

| 91 | PC10   | I/O | FT | SPI0_CS                 | 1553B0_A_IN_EN   | — |

| 92 | PA8    | I/O | FT | TIM1_CH1                | —                | — |

| 93 | PA9    | I/O | FT | TIM1_CH2                | —                | — |

| 94 | VDD    | S   | —  | —                       | —                | — |

| 95 | VSS    | S   | —  | —                       | —                | — |

| 96 | VSS_IO | S   | —  | —                       | —                | — |

| 97 | VDD_IO | S   | —  | —                       | —                | — |

| 98 | PA10   | I/O | FT | TIM1_CH3                | —                | — |

| 99 | PA11   | I/O | FT | TIM1_CH4                | —                | — |

| 10 | PA12   | I/O | FT | TIM1_CH5                | —                | — |

|         |             |     |    |                        |                 |   |

|---------|-------------|-----|----|------------------------|-----------------|---|

| 0       |             |     |    |                        |                 |   |

| 10<br>1 | PA13        | I/O | FT | TIM1_CH6               | —               | — |

| 10<br>2 | VDD         | S   | —  | —                      | —               | — |

| 10<br>3 | VSS         | S   | —  | —                      | —               | — |

| 10<br>4 | VDD_IO      | S   | —  | —                      | —               | — |

| 10<br>5 | PA14        | I/O | FT | DBG_RX                 | —               | — |

| 10<br>6 | PA15        | I/O | FT | DBG_TX                 | —               | — |

| 10<br>7 | PC11        | I/O | FT | SPI0_SCK               | 1553B0_A_IN_P   | — |

| 10<br>8 | PC12        | I/O | FT | SPI0_MISO              | 1553B0_A_IN_N   | — |

| 10<br>9 | VSS         | S   | —  | —                      | —               | — |

| 11<br>0 | VDD         | S   | —  | —                      | —               | — |

| 11<br>1 | PDO         | I/O | FT | SPI0_MOSI              | 1553B0_B_IN_EN  | — |

| 11<br>2 | PD1         | I/O | FT | UART3_TX/1553B0_B_IN_P | -               | — |

| 11<br>3 | PD2         | I/O | FT | UART3_RX               | 1553B0_B_IN_N   | — |

| 11<br>4 | VDD_IO      | S   | —  | —                      | —               | — |

| 11<br>5 | PD3         | I/O | FT | IIC1_SCL               | 1553B0_A_OU_T_P | — |

| 11<br>6 | PD4         | I/O | FT | IIC1_SDA               | 1553B0_A_OU_T_N | — |

| 11<br>7 | PD5         | I/O | FT | SPI2_CS                | 1553B0_B_OU_T_P | — |

| 11<br>8 | PD6         | I/O | FT | SPI2_SCK               | 1553B0_B_OU_T_N | — |

| 11<br>9 | PD7         | I/O | FT | SPI2_MISO              | 1553B0_A_OU_TIN | — |

| 12<br>0 | VSS_IO      | S   | —  | —                      | —               | — |

| 12<br>1 | Dft_Mode[1] | I/O | FT | —                      | —               | — |

| 12      | Dft_Mode[0] | I/O | FT | —                      | —               | — |

|    |             |     |    |           |                    |   |

|----|-------------|-----|----|-----------|--------------------|---|

| 2  |             |     |    |           |                    |   |

| 12 |             |     |    |           |                    |   |

| 3  | Dft_Mode[2] | I/O | FT | —         | —                  | — |

| 12 |             |     |    |           |                    |   |

| 4  | VDD         | S   | —  | —         | —                  | — |

| 12 |             |     |    |           |                    |   |

| 5  | VDD_IO      | S   | —  | —         | —                  | — |

| 12 |             |     |    |           |                    |   |

| 6  | PB6         | I/O | FT | TIMO_CH3  | SPI2_MCS3          | — |

| 12 |             |     |    |           |                    |   |

| 7  | PB5         | I/O | FT | TIMO_CH2  | SPI2_MCS2          | — |

| 12 |             |     |    |           |                    |   |

| 8  | PB7         | I/O | FT | TIMO_CH4  | —                  | — |

| 12 |             |     |    |           |                    |   |

| 9  | BOOT0       | I   | B  | —         | —                  | — |

| 13 |             |     |    |           |                    |   |

| 0  | PB3         | I/O | FT | SPI2_MOSI | 1553B0_B_OU<br>TIN | — |

| 13 |             |     |    |           |                    |   |

| 1  | PB4         | I/O | FT | TIMO_CH1  | SPI2_MCS1          | — |

| 13 |             |     |    |           |                    |   |

| 2  | PB8         | I/O | FT | TIMO_CH5  | —                  | — |

| 13 |             |     |    |           |                    |   |

| 3  | PB9         | I/O | FT | TIMO_CH6  | —                  | — |

| 13 |             |     |    |           |                    |   |

| 4  | VDD_IO      | S   | —  | —         | —                  | — |

| 13 |             |     |    |           |                    |   |

| 5  | VSS         | S   | —  | —         | —                  | — |

| 13 |             |     |    |           |                    |   |

| 6  | PE0         | I/O | FT | IIC2_SCL  | CAN2_RX            | — |

| 13 |             |     |    |           |                    |   |

| 7  | PE1         | I/O | FT | IIC2_SDA  | CAN2_TX            | — |

| 13 |             |     |    |           |                    |   |

| 8  | PE2         | I/O | FT | IIC0_SCL  | SPI1_CS            | — |

| 13 |             |     |    |           |                    |   |

| 9  | VDD         | S   | —  | —         | —                  | — |

| 14 |             |     |    |           |                    |   |

| 0  | PE3         | I/O | FT | IIC0_SDA  | SPI1_SCK           | — |

| 14 |             |     |    |           |                    |   |

| 1  | PE4         | I/O | FT | TIM2_CH5  | SPI1_MISO          | — |

| 14 |             |     |    |           |                    |   |

| 2  | PE5         | I/O | FT | TIM2_CH6  | SPI1_MOSI          | — |

| 14 |             |     |    |           |                    |   |

| 3  | PE6         | I/O | FT | TIM2_CH1  | —                  | — |

| 14 |             |     |    |           |                    |   |

|    | VSS_IO      | S   | —  | —         | —                  | — |

|   |  |  |  |  |  |  |

|---|--|--|--|--|--|--|

| 4 |  |  |  |  |  |  |

|---|--|--|--|--|--|--|

## 5 文档历史版本

| 日期        | 版本   | 变更   |

|-----------|------|------|

| 2023.3.23 | 1.00 | 初始版本 |